The First Official Detail Of Intel Ponte Vecchio Graphics – Up To 128 Xe Core

The First Official Details Of The Graphics (Accelerator) For The Ponte Vecchio Data Center Have Been Released By Intel, Announcing Its Incredible Power.

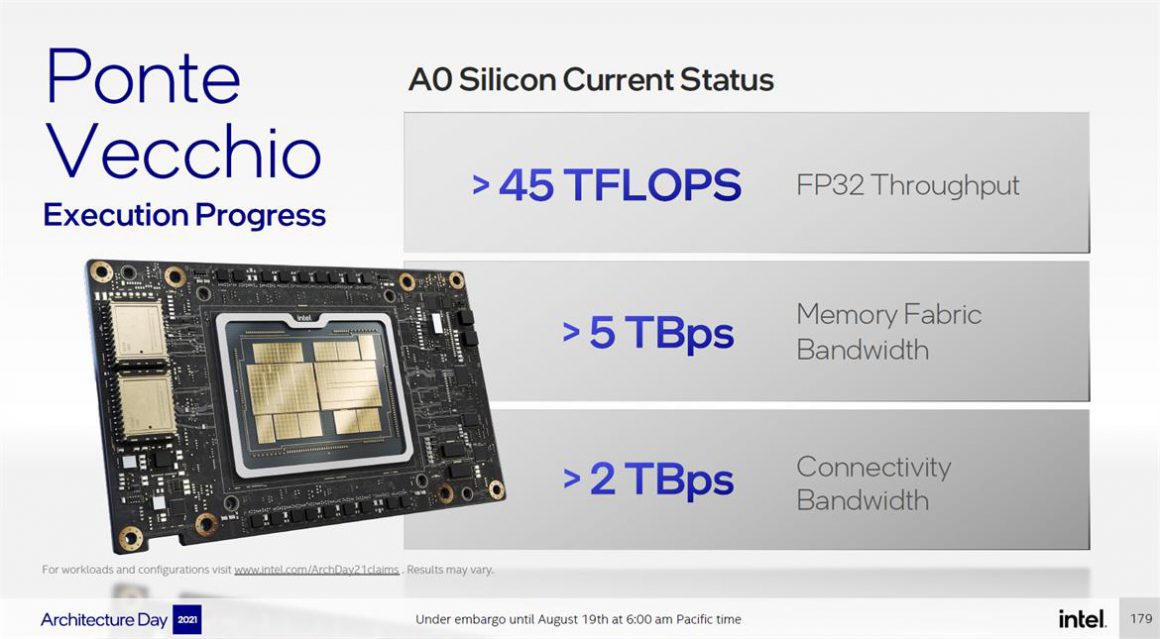

In fact, the company has announced that the silicon A0 version of this accelerator has already reached the computing power of 45 teraflops.

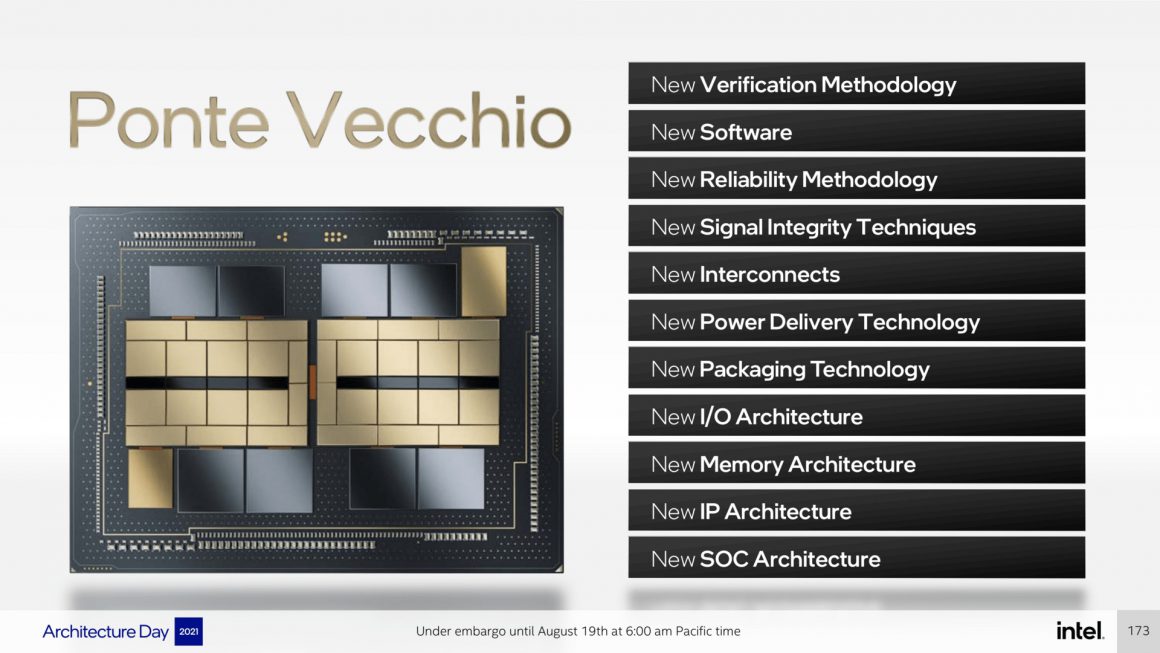

The graphic is the first example of a multi-chip Xe HPC architecture with 47 Tiles with 100 billion transistors.

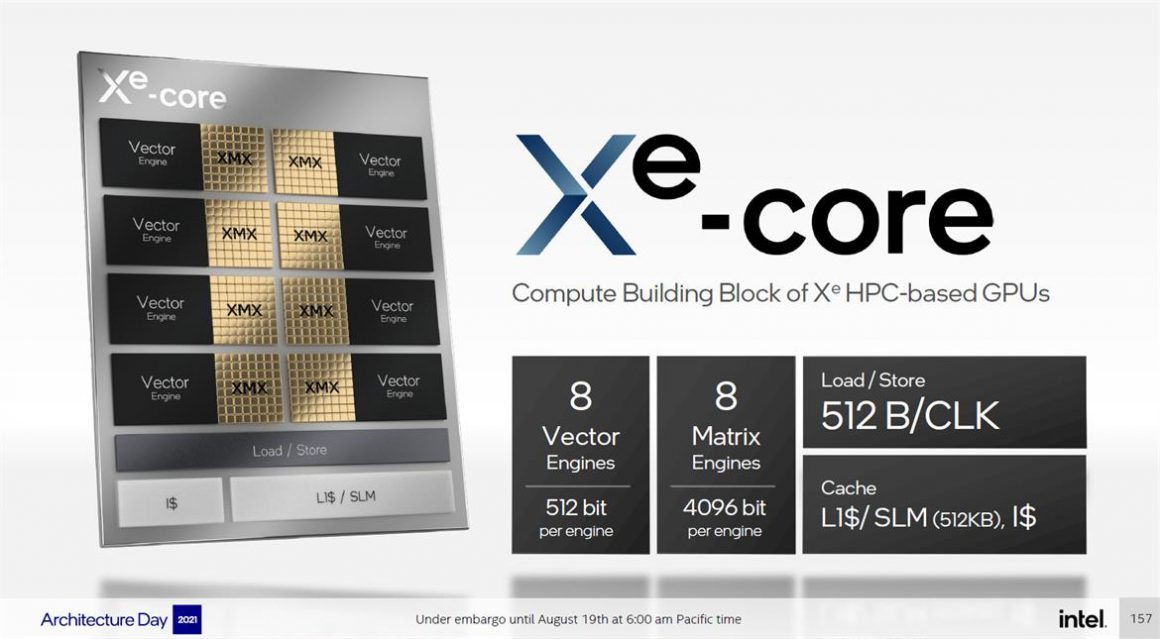

Xe Core Xe HPC architecture uses 8 Vector Engines and 8 Matrix Engines. Compared to Xe HPG, Ponte Vecchio graphics use fewer engines, but they operate on larger busses (512 bits and 4096 bits). These numbers are 256 bits and 1024 bits for HPC, respectively.

The first official details of Intel Ponte Vecchio graphics

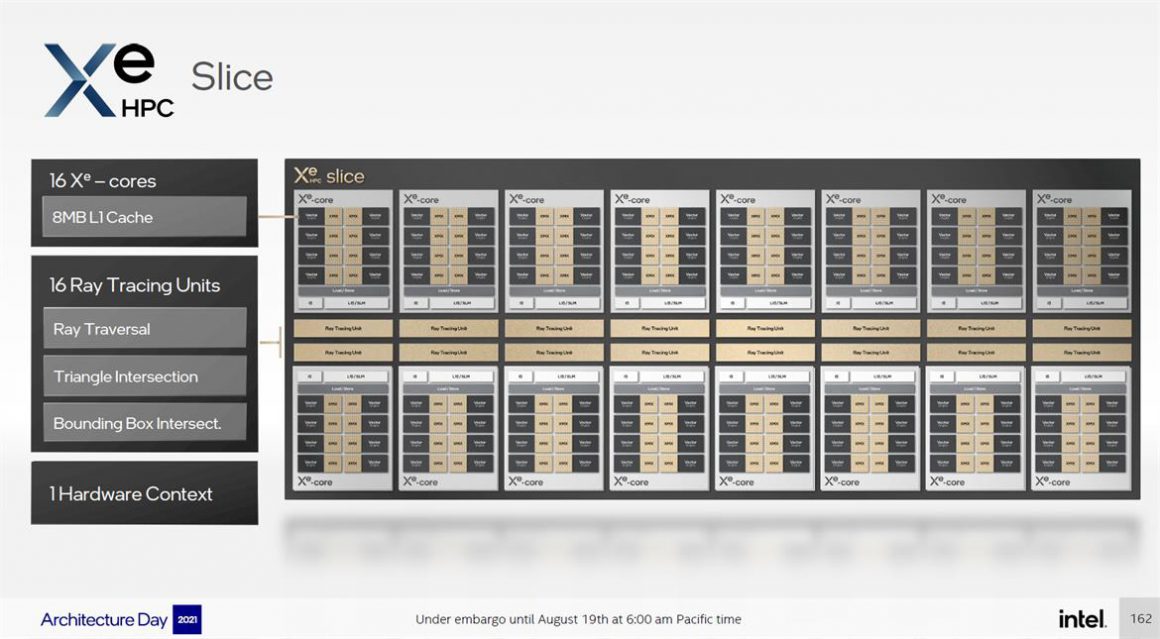

Xe HPC Slice, which will be the main block, has 16 Xe Core. Interestingly, the presence of Ray Tracing Units or beam tracking hardware units in the Ponte Vecchio accelerator. Like the HPG, each Xe Core contains an RT unit. Given that we are dealing with a server accelerator, these cores will not be specifically for gaming.

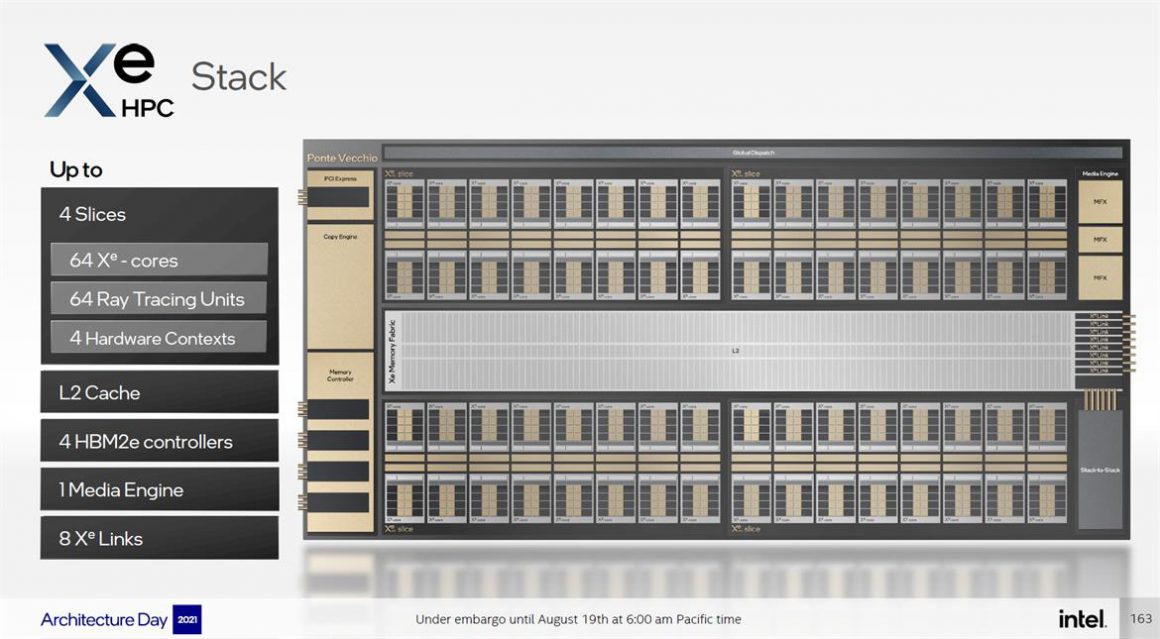

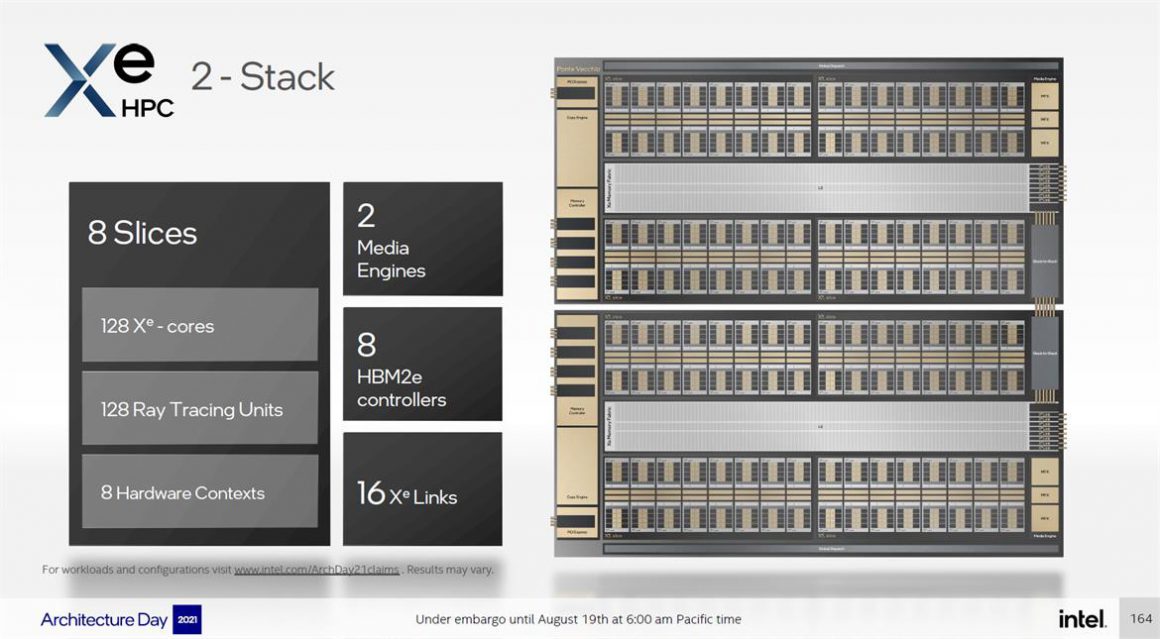

Ponte Vecchio is available in 1 and 2 stack configurations. This means up to 8 cores, 128 Xe Cores, and 128 Ray Tracing Units. The 2-stack configuration also houses eight HBM2E memory controllers.

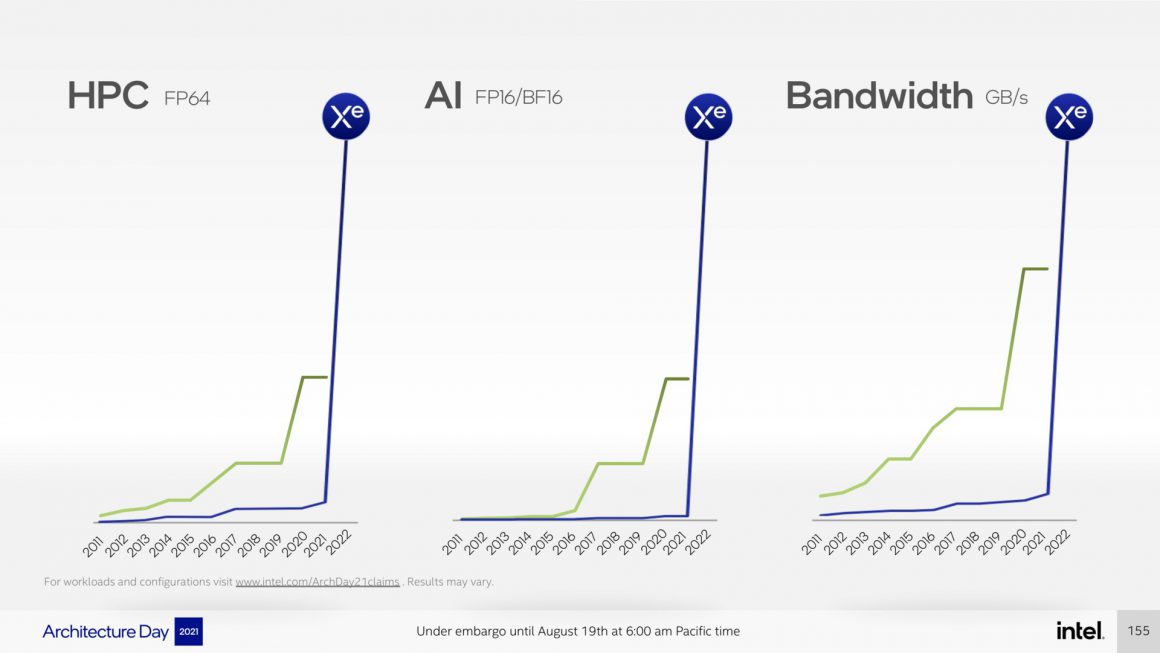

Intel Ponte Vecchio graphics include five nodes called one of the most sophisticated HPC accelerators today. This, of course, can affect the supply of Ponte Vecchio graphics, and the delay of each piece will be equal to the lack of inventory. The blue giant compares its graphics to the Nvidia A100 accelerator, claiming that the FP32 offers twice the performance (45 teraflops vs. 19.5 teraflops). The graphic is currently expected to introduce next year officially.